Samsung Foundry a annoncé qu’elle commençait la production en série de ses puces de première génération sur le nœud 3 nm. Il est basé sur la nouvelle architecture de transistor GAA (Gate-All-Around), qui est la prochaine étape après FinFET.

Par rapport au 5 nm, les puces 3 nm de première génération de Samsung peuvent fournir jusqu’à 23 % de meilleures performances, jusqu’à 45 % de réduction de la consommation d’énergie et une réduction de 16 % de la surface.

Le nœud 3 nm de deuxième génération de Samsung sera encore plus impressionnant – par rapport au 5 nm, Samsung prétend qu’il permettra d’obtenir une réduction de 50 % de la consommation d’énergie, jusqu’à 30 % d’amélioration des performances et une réduction de 35 % de la surface.

Samsung devance désormais TSMC, qui devrait commencer la production de masse de puces 3 nm au second semestre.

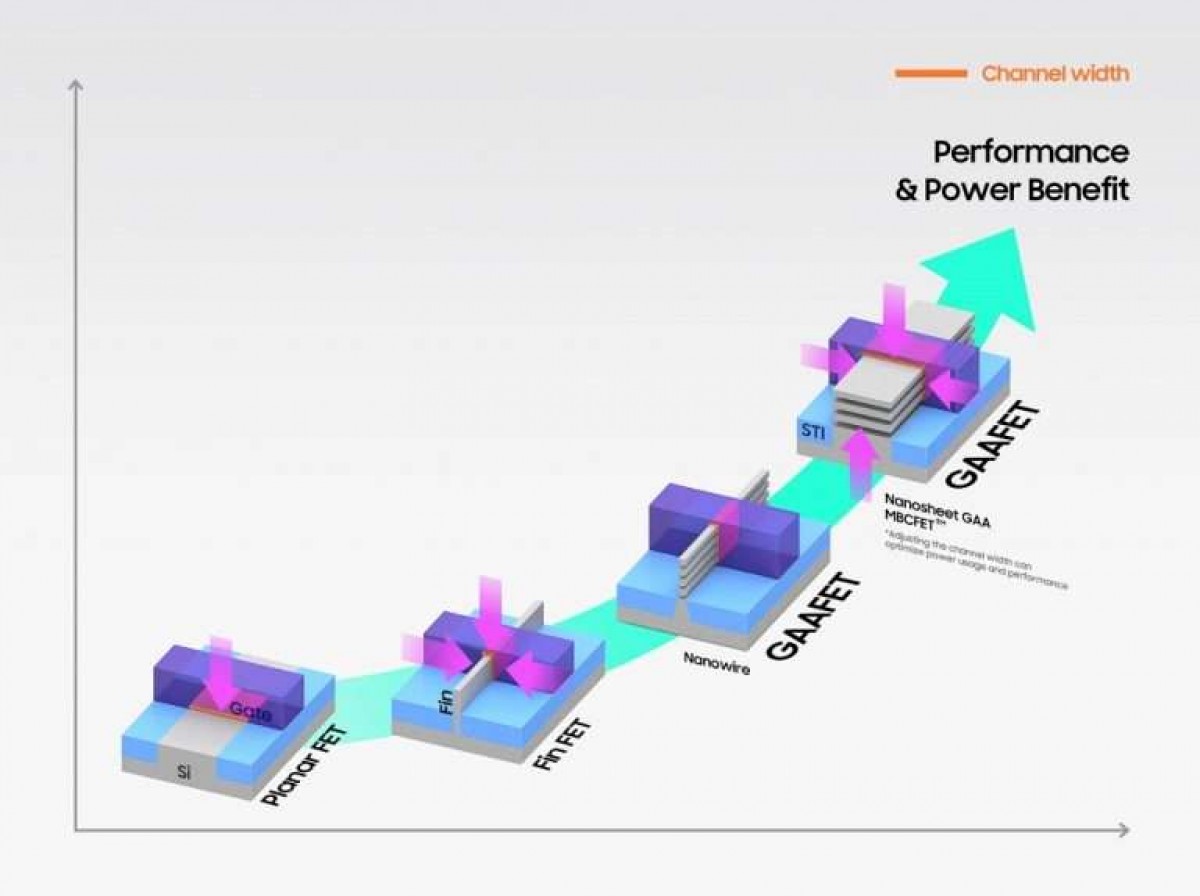

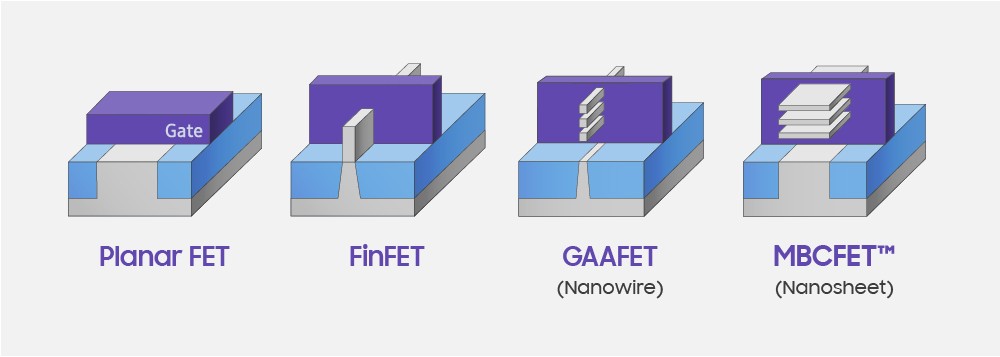

La conception des transistors Gate-All-Around (GAA) permet à la fonderie de rétrécir les transistors, sans nuire à leur capacité à transporter le courant. La conception GAAFET utilisée dans le nœud 3 nm est la version MBCFET illustrée dans l’image ci-dessous.

L’évolution des transistors au silicium

L’évolution des transistors au silicium